## Special Feature: RENA-CHIP—An LSI for High-

# **Technical Trends of Network Processors and the RENA-CHIP**

### Keiichi Koike<sup>†</sup>

#### Abstract

This article describes the background for the development of the RENA-CHIP, which provides highperformance quality control and firewall functions for 1-Gbit/s network access.

#### 1. Introduction

NTT Cyber Solutions Laboratories has developed a dedicated LSI (large-scale integration) chip for handling the 1-Gbit/s access speed of future network services. RENA (resonant communication network architecture) is NTT's concept for the next-generation optical network architecture [1]. In choosing a name for our chip, which will play a vital role in RENA, we decided upon RENA-CHIP<sup>\*</sup> because RENA can also stand for routing engine for next-generation network access. This chip is a low-cost LSI for processing communication functions such as firewall functions and quality control at a transmission speed of 1 Gbit/s in both the upward and downward directions, even under conditions of high communication load. Hardware implementation of functions that were economically difficult to implement with conventional software processing was achieved through a combination of both high performance and low cost for the first time. This article describes the development and policy of the RENA-CHIP (Fig. 1).

#### 2. Importance of IP processing performance

The communication protocol used on the Internet, TCP/IP (transmission control protocol Internet protocol, or simply IP), is now being used in many communication platforms. Communication tasks ranging from private party network access to communication within and between enterprises are all performed by

Fig. 1. External view of the RENA-CHIP.

basically the same procedure. This conversion to IP technology is extending even to the telephone service, which has basically continued to be provided by the same method since its birth over 100 years ago.

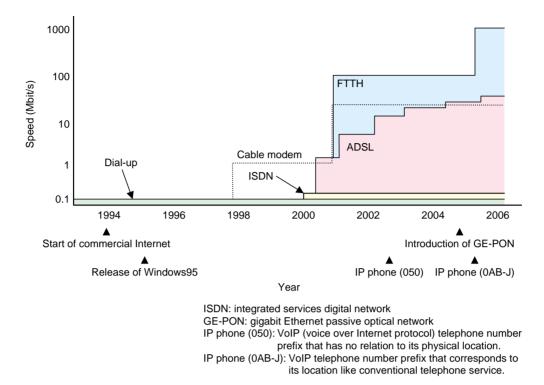

While IP has penetrated to the point of changing the entire basis of the network, in the beginning it was just barely powerful enough for connecting to the Internet. The bandwidth was narrow and unstable, and its application to the transmission of voice or video was unimaginable. Later, ADSL (asymmetric digital subscriber line), cable TV, and then FTTH (fiber to the home) dramatically increased the usable access network bandwidth. With FTTH, IP telephone service using the same 0AB-J numbers as the fixedline telephone network has begun (**Fig. 2**).

Was IP telephone service made possible by the increase in the usable bandwidth? The bandwidth required for telephony is 100 kbit/s at most, so it does not require the whole bandwidth provided by FTTH, which is currently up to 100 Mbit/s. Actually, the key to making IP telephony capable of the same service as fixed-line telephony is quality of service (QoS). Conventional fixed-line telephony is capable of stable

<sup>†</sup> NTT Cyber Solutions Laboratories Yokosuka-shi, 239-0847 Japan E-mail: koike.keiichi@lab.ntt.co.jp

RENA-CHIP is a registered trademark of NTT Electronics Corporation.

Fig. 2. Changes in Internet access in Japan.

communication with a dedicated bandwidth of 64 kbit/s for each call and with circuit switching. In an IP network, on the other hand, diverse types of communication are generally performed over the same network in order to reduce communication costs. Thus, voice data in the form of an IP packet may be affected by other types of communication, resulting in delays and data loss that reduce voice quality. There is a specification for setting the priority of an IP packet in the packet header (type of service in IPv4 and traffic class in IPv6). The network that transmits the packets processes them appropriately based on that priority information, thus providing the required quality according to the service content. IP telephony via FTTH achieves a quality that is not inferior to conventional telephony by making use of both the stable communication characteristics of optical fiber and the priority handling of voice communication in the network.

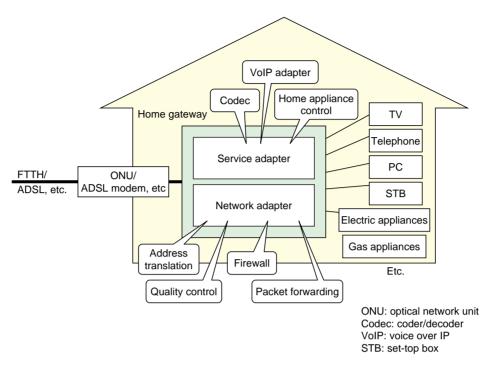

Using an IP network that takes QoS into account makes it possible to implement services that have previously been difficult to implement. For example, 1-Gbit/s FTTH is capable of transmitting the data contained in one CD (compact disk) within just 10 seconds, so the distribution of multichannel HDTV (high-definition television) video is no longer just a dream. The home gateway makes such IP network services available in the home (**Fig. 3**). It has the functions of a network adapter (i.e., the functions of a device generally known as a broadband router) for lower-layer network processing and the functions of a service adapter for relaying or terminating services (**Table 1**).

Ordinary network adapters that are currently available assign host addresses and translate addresses, transmit packets, and have simple firewall functions. They work with the 100-Mbit/s IPv4 network. The embedded CPU (central processing unit) in the network adapter or a network processor that enhances the communication functions of the CPU are configured to optimize the above functions and processing speed, so the performance will be insufficient for the diverse services expected in the future. Basically, the packet transmission, firewall, and QoS functions will have to be supported at a speed of 1 Gbit/s. In IP telephony, packet lengths are set to a short value to reduce delay. These short packets carry the same amount of data as long ones would, but they require a larger number of processing iterations, so the processing load increases, when the transmission speed is high, such as 1 Gbit/s. Therefore, the network processor is required to have a high performance.

Fig. 3. Home gateway functions.

| Table 1. | Main functions of a home gate | way. |

|----------|-------------------------------|------|

|----------|-------------------------------|------|

| Network adapter functions                   | Service adapter functions                                 |

|---------------------------------------------|-----------------------------------------------------------|

| <ul> <li>Host address assignment</li> </ul> | VoIP adapter                                              |

| <ul> <li>Address translation</li> </ul>     | Video codec                                               |

| Quality control                             | <ul> <li>Signaling such as SIP</li> </ul>                 |

| • Firewall                                  | <ul> <li>Local protocol conversion<sup>*</sup></li> </ul> |

| <ul> <li>Packet forwarding</li> </ul>       | Control of electrical and gas appliances                  |

| <ul> <li>Encryption/decryption</li> </ul>   | User authentication                                       |

| <ul> <li>Line authentication</li> </ul>     | <ul> <li>Wireless access point</li> </ul>                 |

\* Electrical power line communication, ECHONET, IEEE1394, etc. SIP: session initiation protocol

#### 3. Network processors

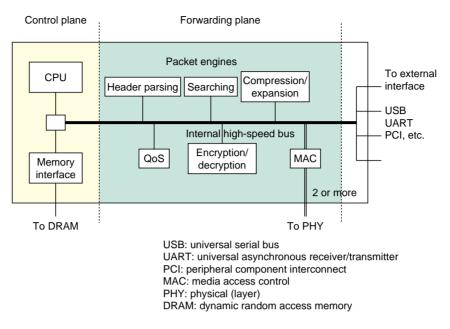

Because processing capability is especially important in large-scale routers such as those used by Internet service providers, dedicated application-specific integrated circuit (ASIC) chips are used in them. One weak point of ASIC implementations, however, is inflexibility with respect to changes in processing. Network processors began as a solution to that problem by integrating a CPU and dedicated packet processing hardware to achieve programmable processing. Later, high performance also came to be required in consumer-oriented equipment such as broadband routers, and some equipment with network processor configurations involving dedicated packet processing hardware has appeared. A typical network processor configuration is illustrated in **Fig. 4**. Parsing of the packet header, searching, QoS, encryption/decryption and other such processing is comparatively simple, but it involves many iterations, so it creates a heavy processing load. Therefore, these functions, which are referred to as the forwarding plane functions, are implemented in dedicated hardware (packet engines). Processing such as table management and address assignment is comparatively difficult, but infrequent, so the processing load is relatively low. These functions are referred to as the control plane functions and they are executed by the embedded CPU, which is an economical device that omits a number of hardware functions.

The CPU and the various packet engines are inter-

Fig. 4. General configuration of the network processor.

connected by an internal high-speed bus, which is an effective configuration for optimum processing speed. Some network processors are also equipped with programmable packet engines for which functions can be defined by microcode, thus providing both the speed of hardware processing and the flexibility of software processing.

Using network processors that can reduce the development period for responding quickly to new network services as they appear has become an appropriate solution. The network processor is likely to be an important component for various other network devices in addition to routers.

#### 4. Positioning of the RENA-CHIP

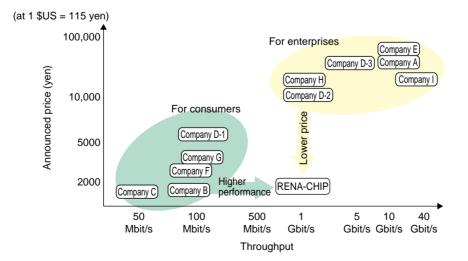

The performances and price ranges of the main network processors are shown in **Fig. 5**. The current network processor market is split into enterprise-oriented 1-Gbit/s products and consumer-oriented 100-Mbit/s products, as higher- and lower-class products, respectively. This split probably results from the fact that, while service providers and other commercial enterprises required performance above 1 Gbit/s to handle with the traffic in the early period of market development, consumer requirements for performance advanced in stages as new access methods

Fig. 5. Main network processor performance values and price ranges.

were introduced, beginning with dial-up access and progressing to ADSL, cable modem, and then FTTH. Another reason is that the user-side bandwidth for broadband service is generally 100 Mbit/s at most, so competition based on speed fell off when 100 Mbit/s was reached. Furthermore, conventional Internet connection service rarely provides a quality control service, so up to now network adapters have not implemented QoS functions and the packet filtering function required by the firewall is also simple. Thus, network processor products are separated into two groups by both price and function.

If FTTH becomes a 1-Gbit/s QoS network for safe and reliable provision of the kind of high-quality services expected to arrive with the future NGN (Next Generation Network), what should be used for the network processor of the home gateway? It would be very difficult to improve on a network processor designed to handle 100 Mbit/s so as to achieve a tenfold increase in speed; it would probably require a fundamental revision of the device structure. On the other hand, using an enterprise-oriented network processor for consumer applications would create problems of cost and power consumption. The RENA-CHIP was developed to solve this dilemma. It is an ASIC for use in the home gateway. It can handle transmission speeds of 1 Gbit/s and is priced for consumer applications. Physically, the network processor structurally separates the packet engine parts and has an interface for communicating with the CPU that performs the table management and other control processing. This approach is based on the design policy that it should be possible to select the optimum CPU in terms of performance and cost in accordance with the assets of the home gateway developer and the required software specifications.

Our chip's functions are explained in detail in the following articles in this Special Feature. In summa-

ry, the RENA-CHIP is capable of 1-Gbit/s wire-rate (the maximum output speed of the interface, regardless of packet length) processing in both the upward and downward directions simultaneously regardless of the user's usage circumstances. Processing that is only partially implemented in other network processors used in consumer-oriented products, such as the types of processing listed below, can be performed by dedicated hardware engines in the RENA-CHIP.

- Header parsing and searching

- QoS control

- Filtering

- IPsec (IP security provided by IPv6 encapsulation)

- Packet forwarding

- Frame generation

The RENA-CHIP is superior to competing network processors in performance, cost, and power consumption. We expect it to serve as a powerful key device for the home gateway in the NGN and become an impetus for better services.

#### Reference

[1] N. Wada, "Ushering in a New Networked Society," NTT Technical Review, Vol. 2, No. 4, pp. 6-13, 2004.

#### Keiichi Koike

Senior Research Engineer, Supervisor, First Promotion Project, NTT Cyber Solutions Laboratories.

He received the B.E. and M.E. degrees in electronic engineering from Osaka University, Osaka, in 1985 and 1987, respectively. He joined NTT LSI Laboratories, Kanagawa, in 1987. He has been engaged in research on the design of high-speed LSIs and IP appliances. He is a member of the Institute of Electronics, Information and Communication Engineers of Japan.